Arm Cortex M4 Instruction Set

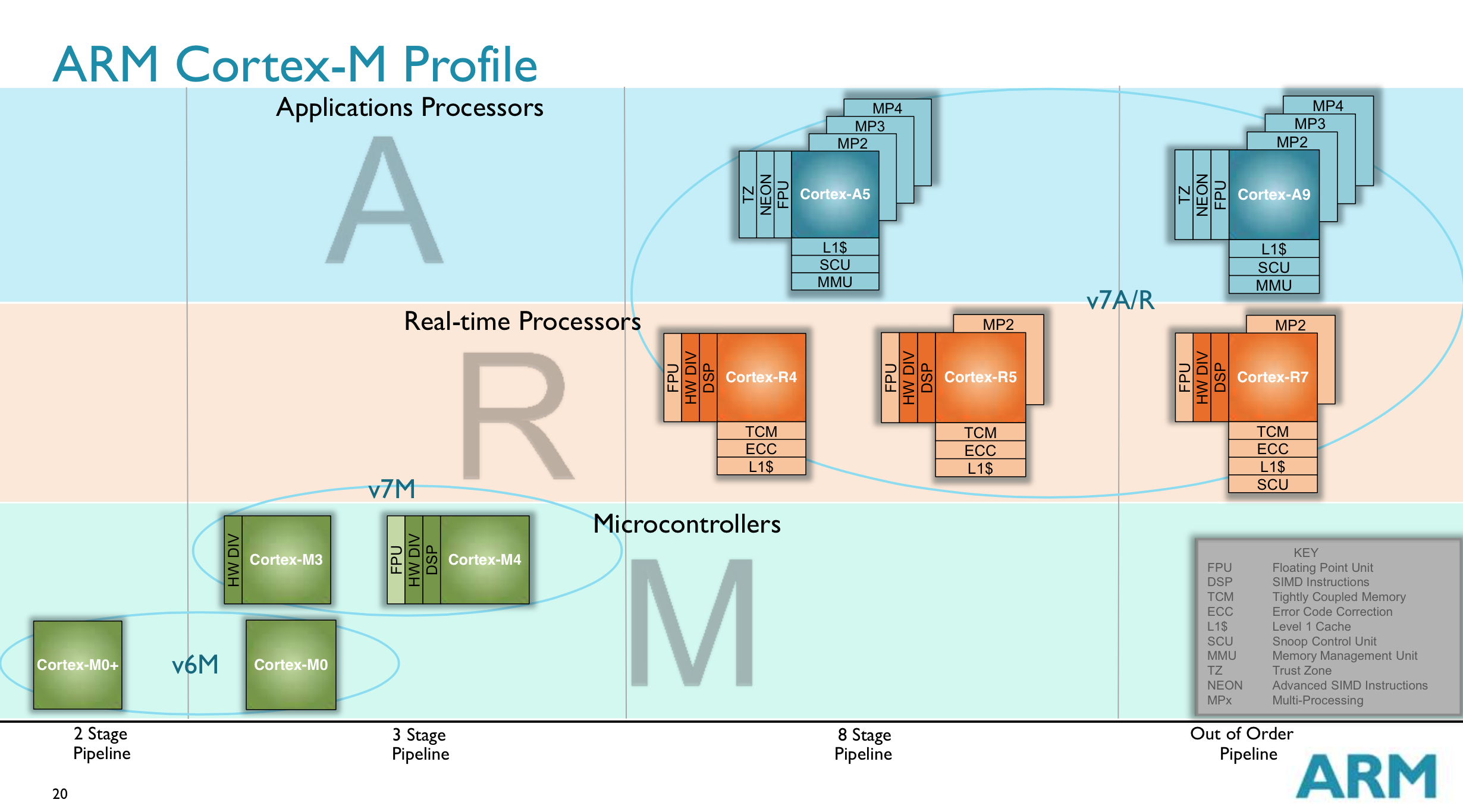

This is a list of microarchitectures based on the ARM family of instruction sets designed by ARM Holdings and 3rd parties, sorted by version of the ARM instruction set, release and name In 05, ARM provided a summary of the numerous vendors who implement ARM cores in their design Keil also provides a somewhat newer summary of vendors of ARM based processors.

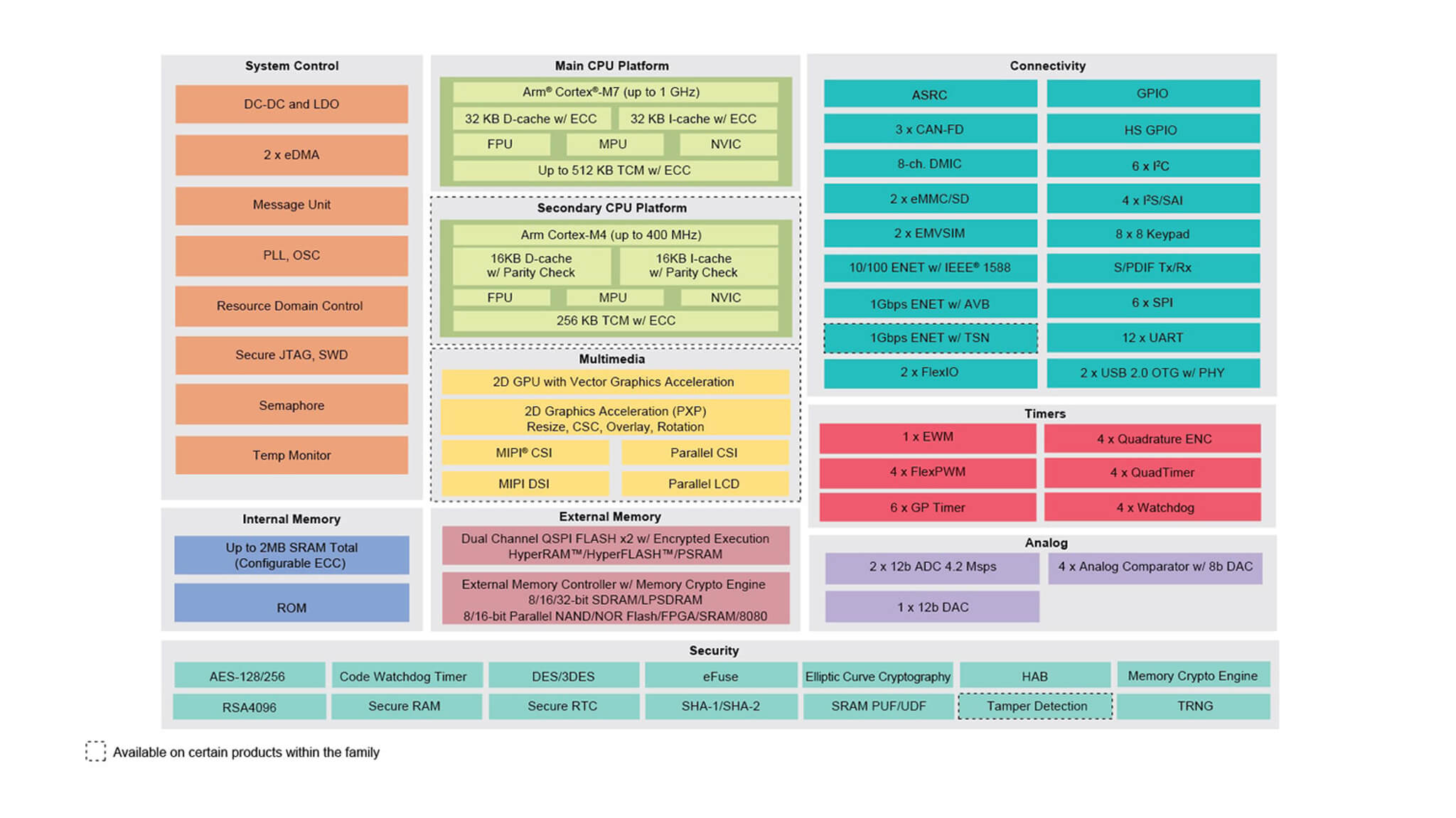

Arm cortex m4 instruction set. MCU communication Interfaces 3 x SPI, 4 x USART, 2 x UART, 2 x I2S, 3 x I2C;. Developers It gives a full description of the STM32 Cortex®M4 processor programming model, instruction set and core peripherals The applicable products are listed in the table below The Cortex®M4 processor used in STM32F3 Series, STM32F4 Series, STM32G4 Series, STM32H745/755 and STM32H747/757 Lines, STM32L4 Series, STM32L4 Series,. The hardware supports ARM_CM4F but the instruction set used in the file mentioned above relates to ARM_CM7 which causes a problem caused by incorrect command line options being passed to the compiler if this is the CortexM4 core of that part If you don’t tell the compiler the device has a floating point unit then the assembler will.

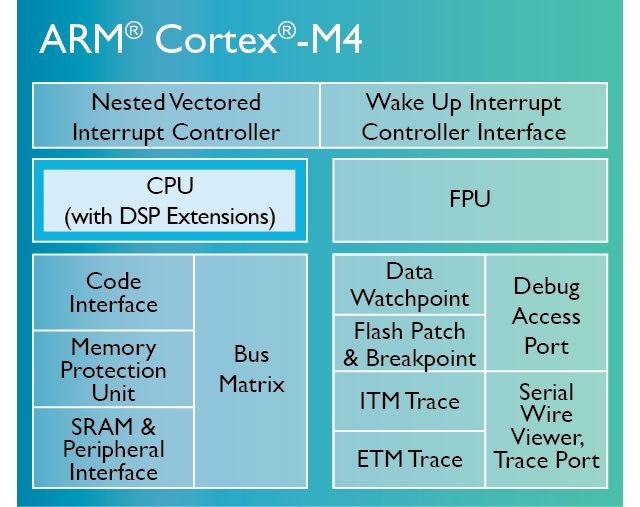

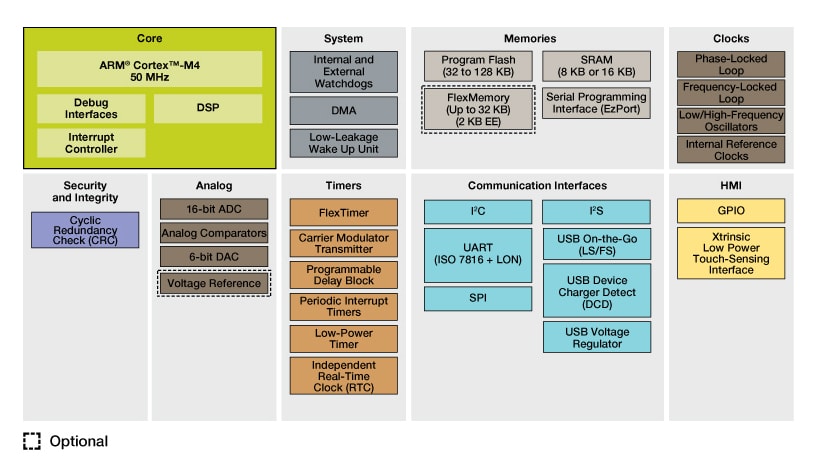

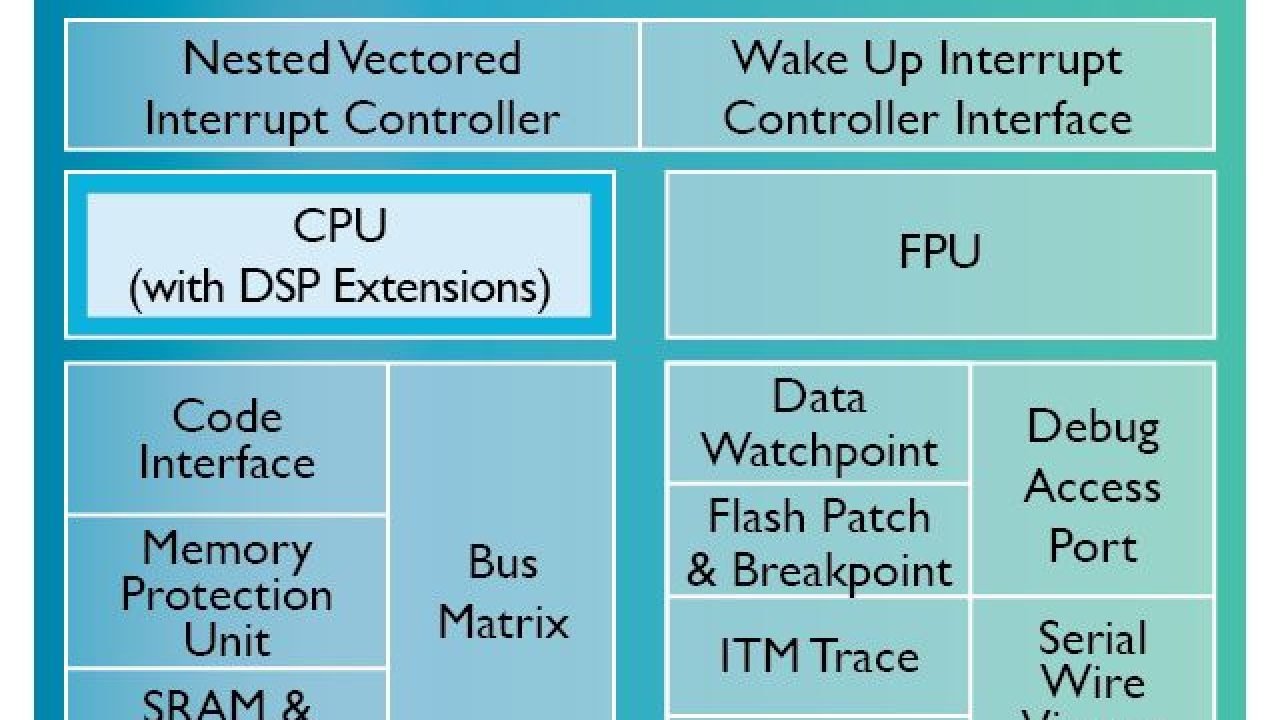

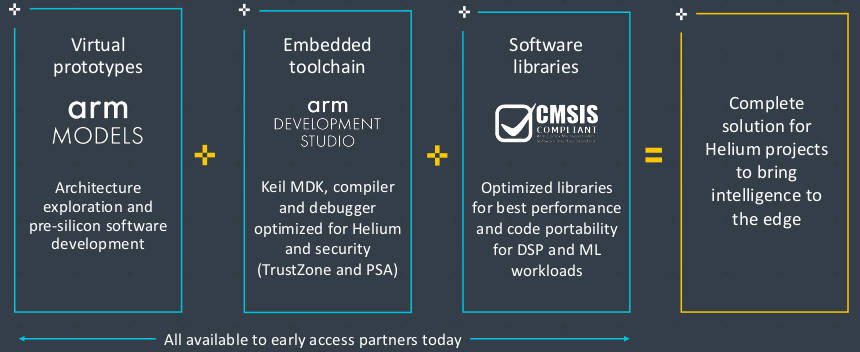

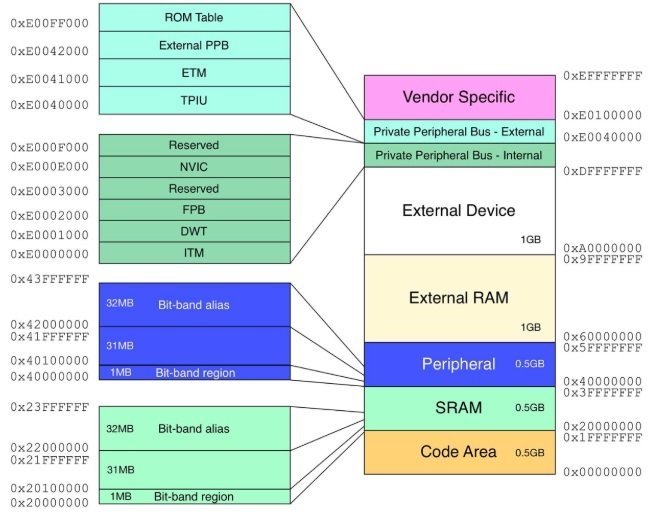

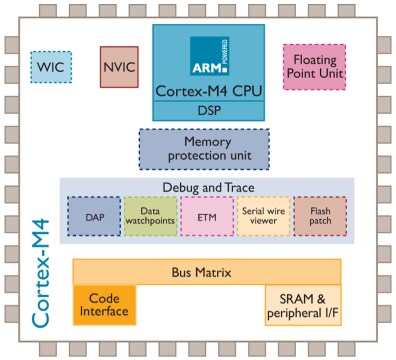

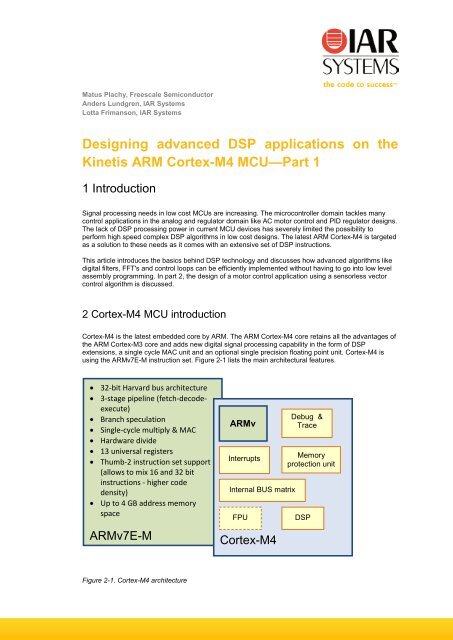

ARM CortexM4 Technical Reference Manual (TRM) This guide contains documentation for the CortexM4 processor, the programmer s model, instruction set, registers, memory map, floating point, multimedia, trace and debug support Components include ETM, MPU, NVIC, FPB, DWT, ITM, AHB, TPIU, VFP. 1 x FSMC, 1 x SDIO, 2 x CAN. SAMG5x – ARM CortexM4F core, which includes FPU, ATSAMG55 for 1MHz CPU speed SAMD5x Latest ARM CortexM4F core, which includes FPU and Integrated Security including Symmetric (AES) and Asymmetric (ECC) Encryption, Public Key Exchange Support(PUKCC), TRNG and SHA based memory Integrity checker.

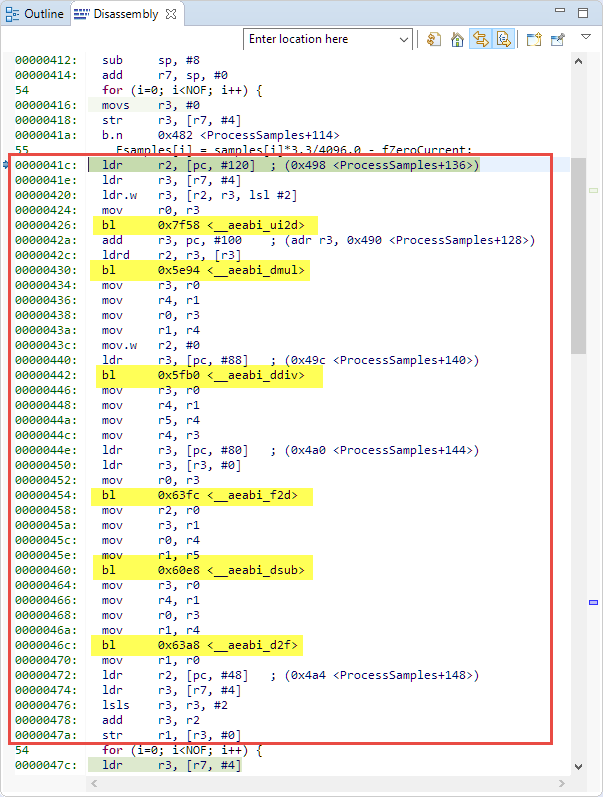

The compiler will inject specific replacement routines which take more time to compute. I would like to count the number of Instructions per Cycle executed on an ARM cortexM4 (or cortexM3) processor What it's needed is number of instructions (executed at runtime) of the code I want to profile and number of cycles that the code takes to execute 1 Number of Cycles Use the cycle counter is quite easy and straightforward. Memories 1024kB Flash, 1924kB SRAM;.

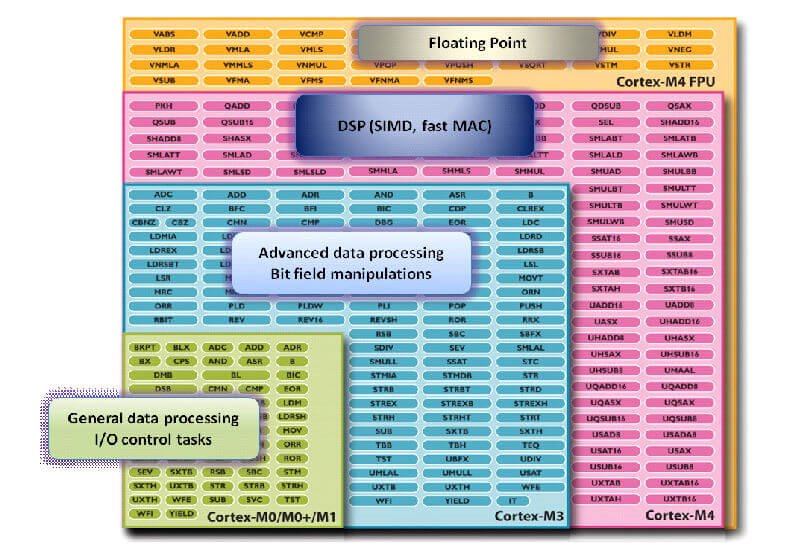

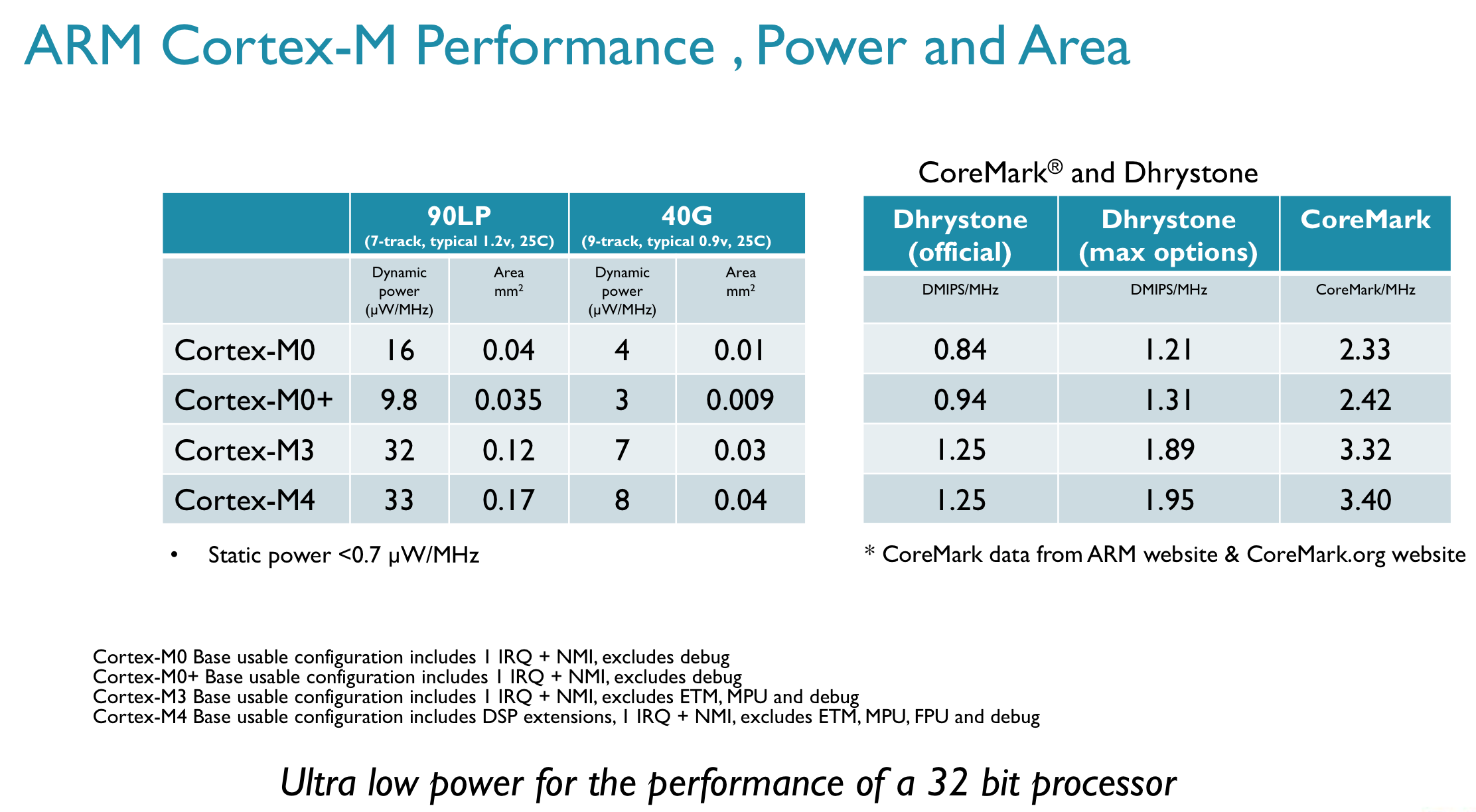

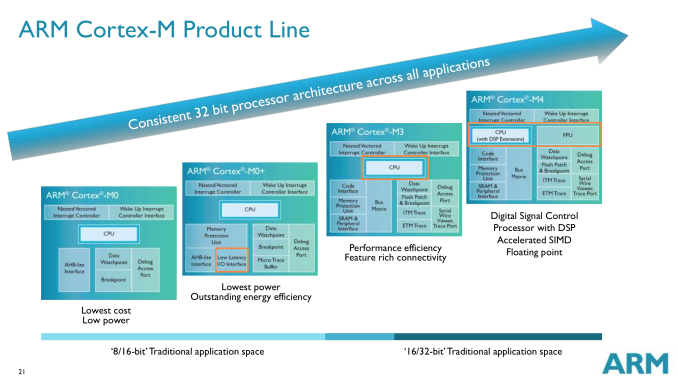

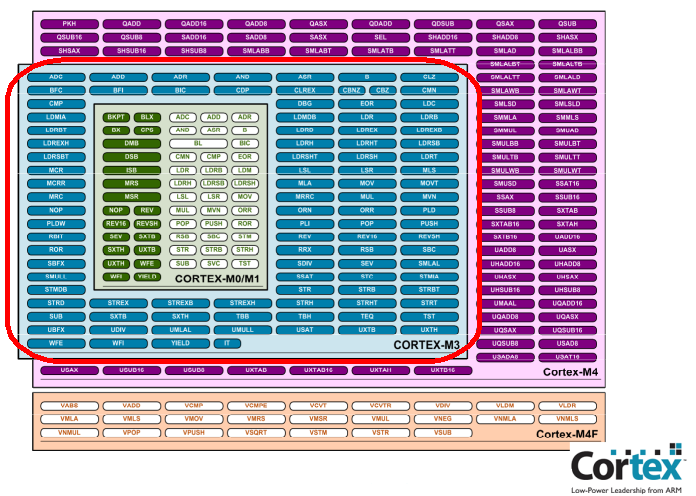

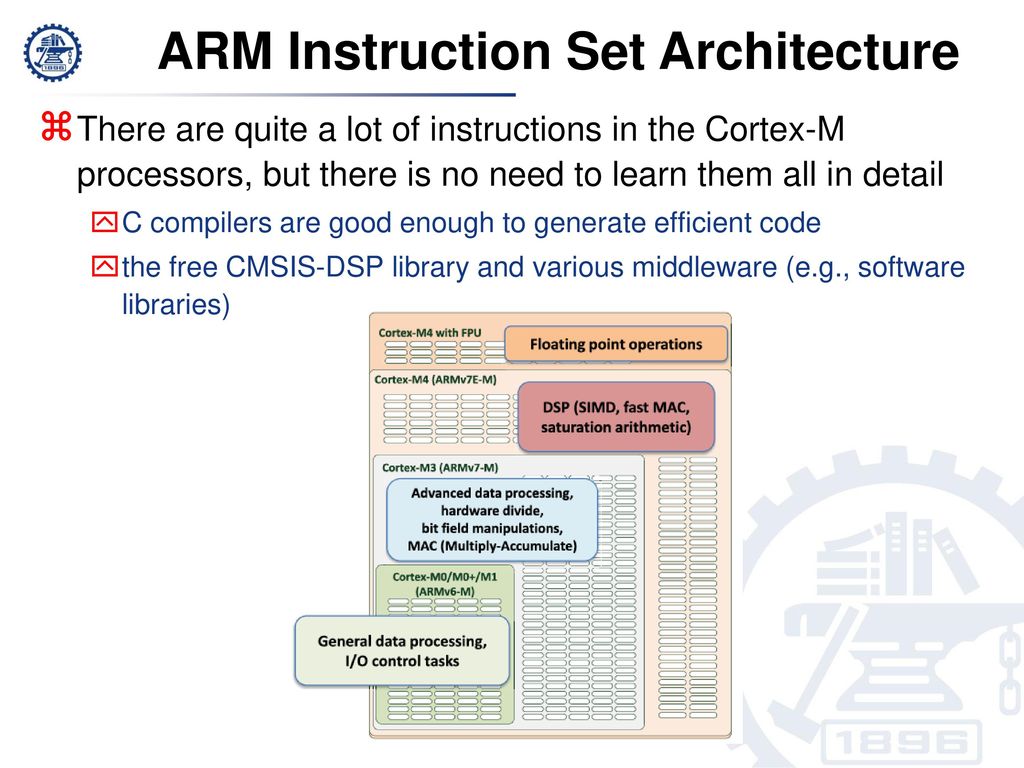

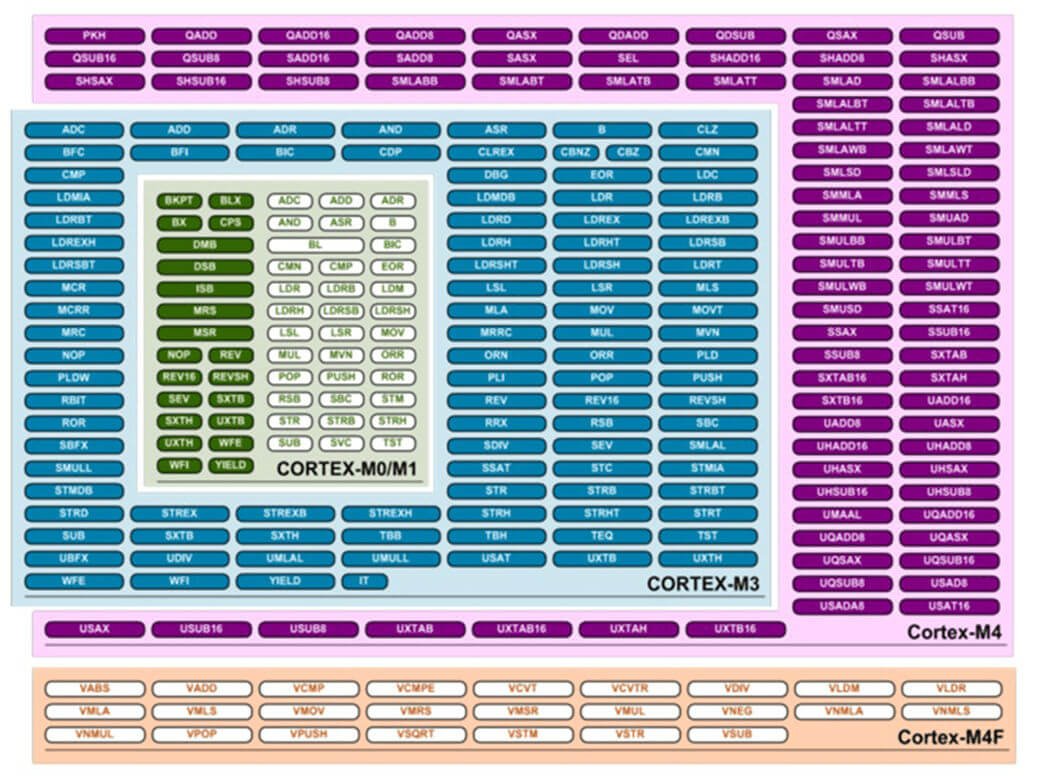

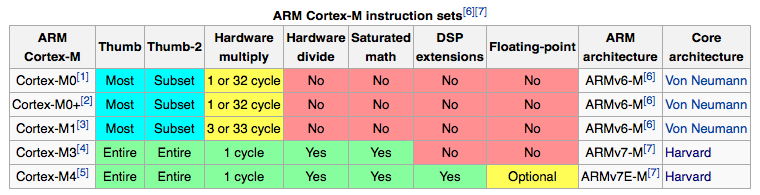

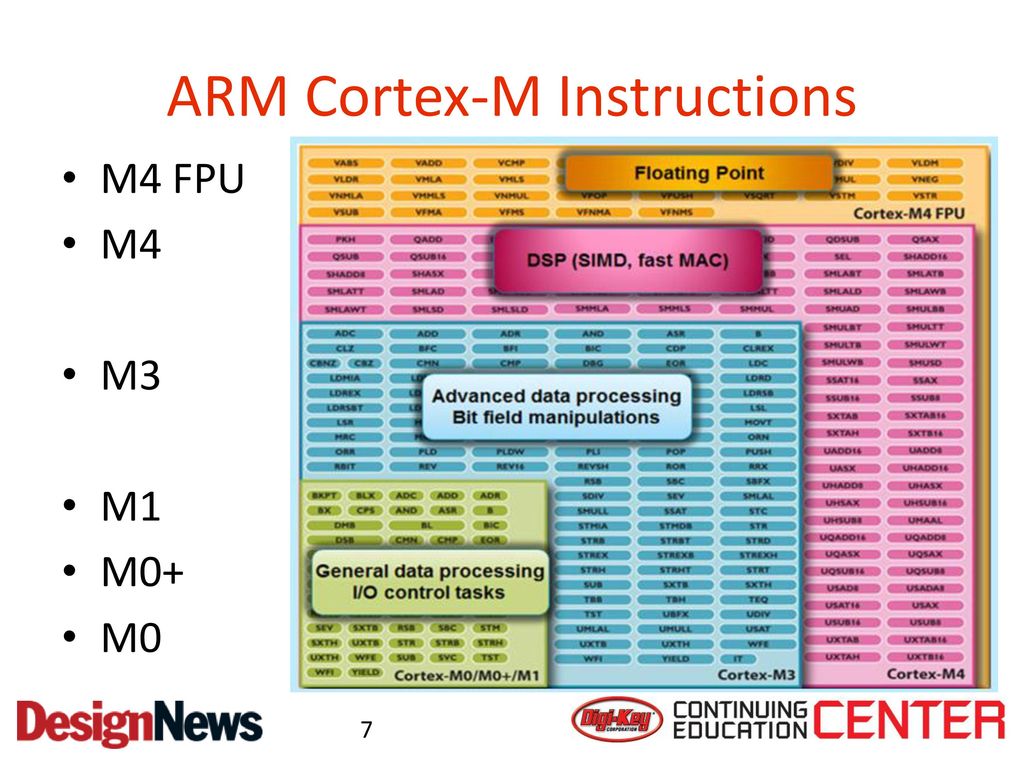

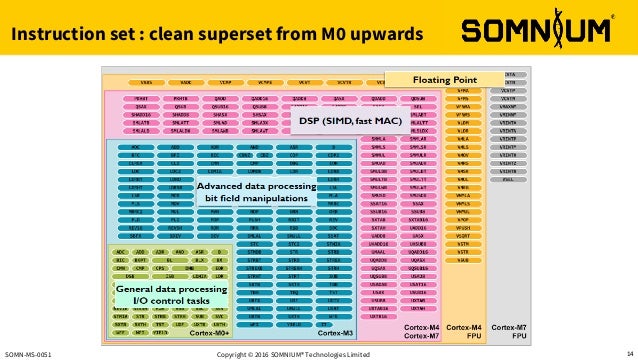

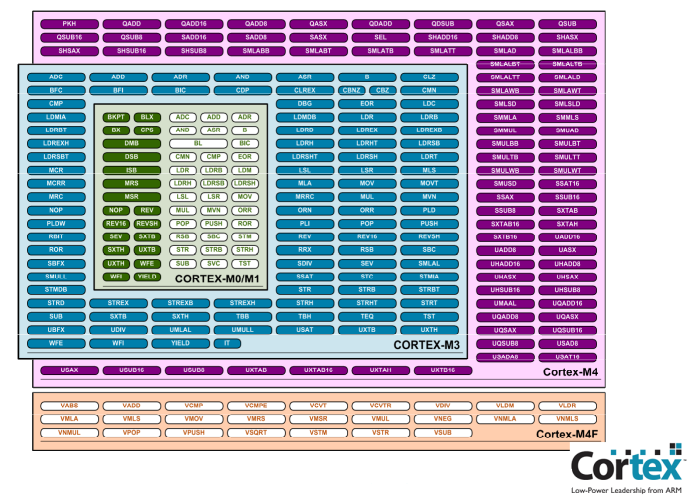

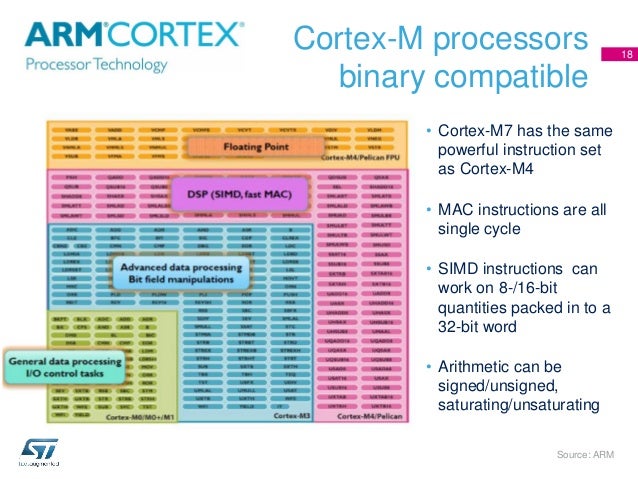

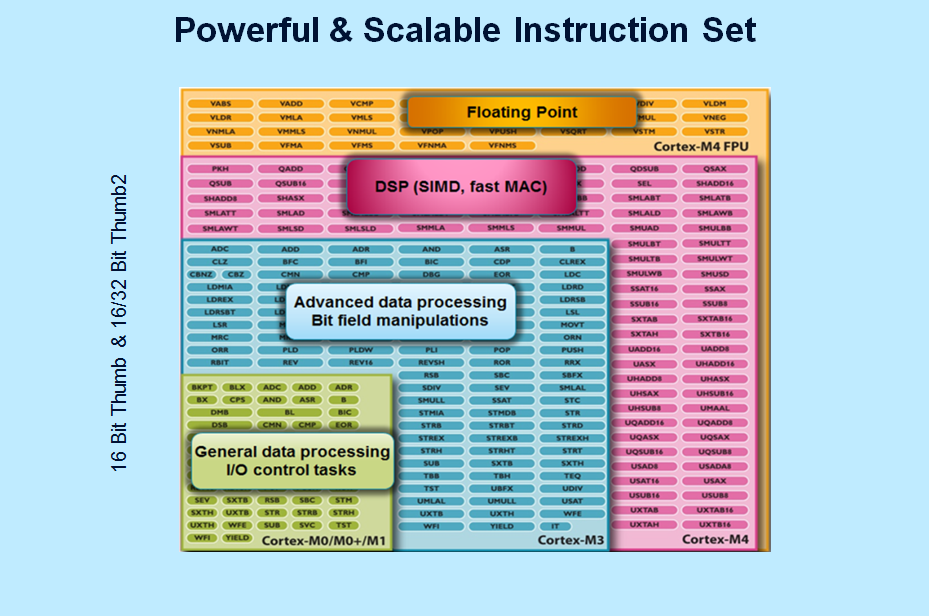

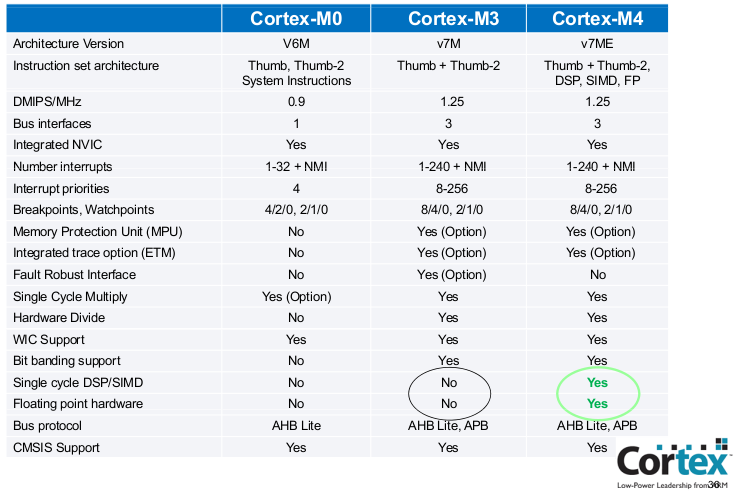

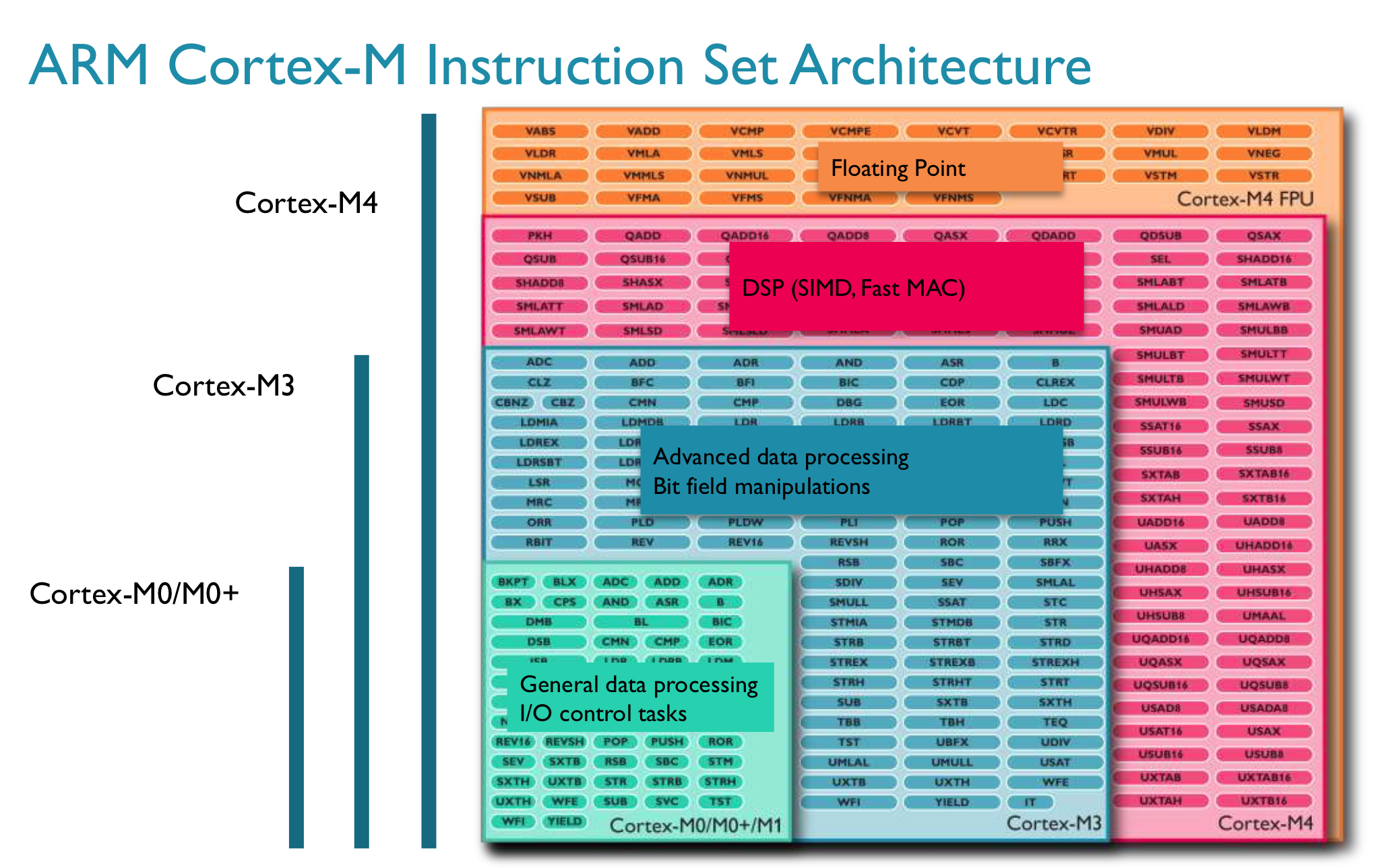

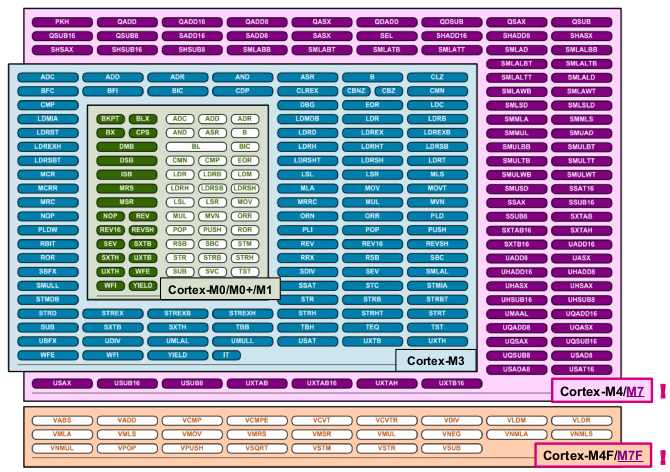

ARM CortexM4 packs even more processing power as compared to M3 It adds 'SMID' (single instruction multiple data) instructions, and completes some instructions in single clock cycle as compared to multi clock cycle execution in M3 Its suitable for adding DSP applications to your SoC. The STM32 CortexM4 instruction set PM0214 50/260 DocID Rev 5 AND, ANDS {Rd,} Rn, Op2 Logical AND N,Z,C 352 on page 84 ASR, ASRS Rd, Rm, Arithmetic shift right N,Z,C 353 on page 85 B label Branch — 395 on page 141 BFC Rd, #lsb, #width Bit field clear — 391 on page 138 BFI Rd, Rn, #lsb, #width Bit field insert — 391 on page 138. ARM CortexM ARM Cortex M is a family of 32 bit microprocessors, which was developed by the company ARM and is produced under license from various hardware manufacturers The core is a reduced instruction set computer (RISC ) that is part of the ARMv6 architecture and is divided in ascending complexity in the units Cortex M0, Cortex M0 , Cortex M1, Cortex M3 and Cortex M4.

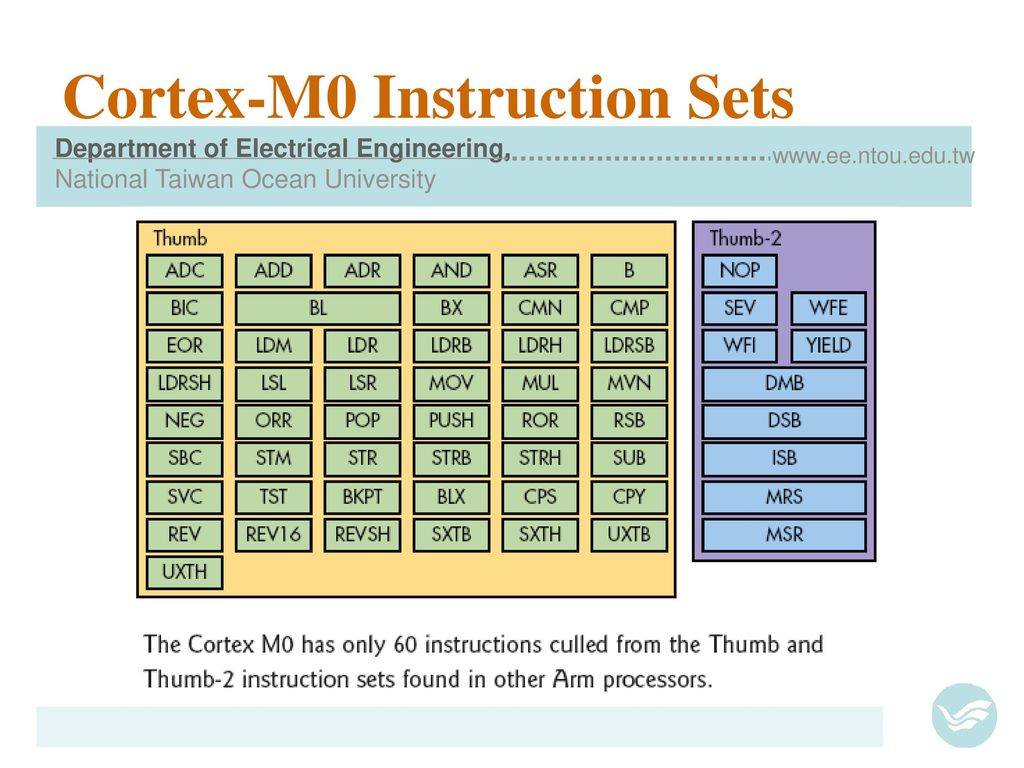

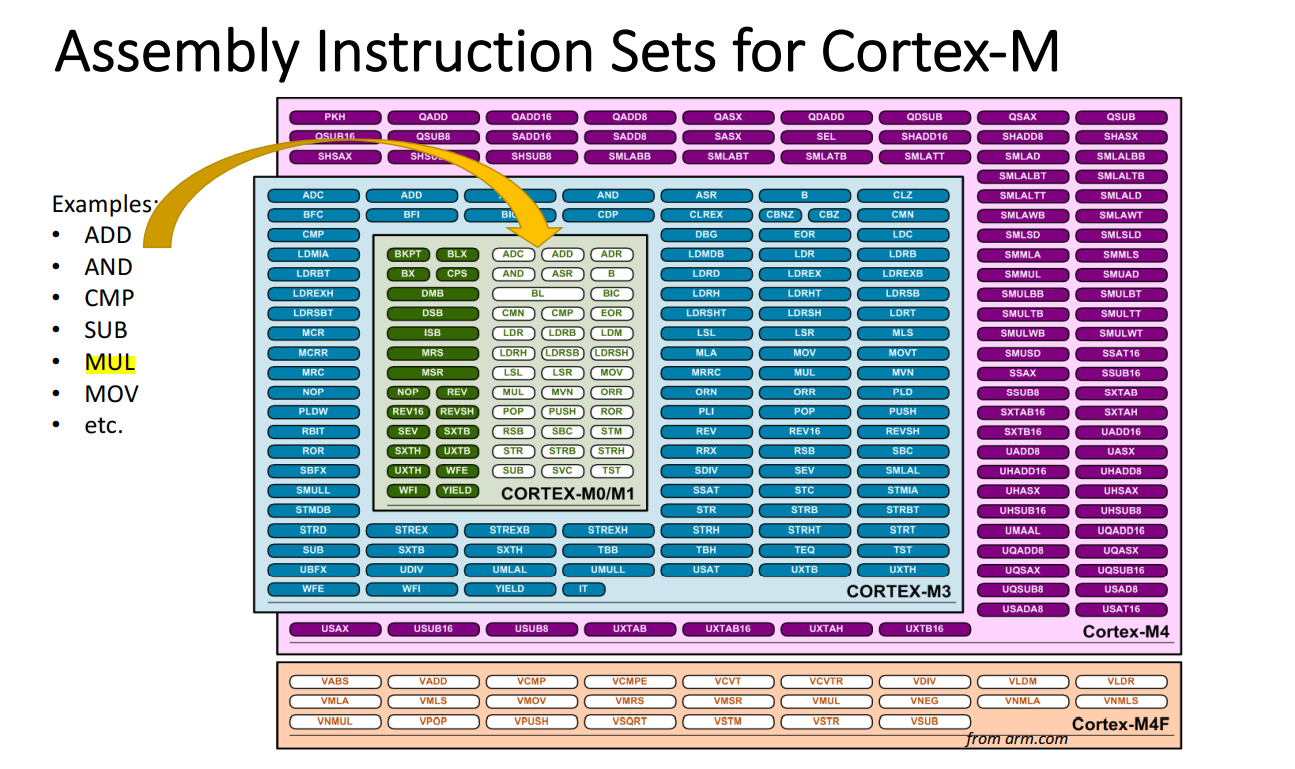

Home ARM CortexM Assembly Instructions ARM CortexM Assembly Instructions NOTE Ra Rd Rm Rn Rt represent 32bit registers value any 32bit value signed, unsigned, or address {S} if S is present, instruction will set condition codes #im12 CortexM4 Tiva C Launchpad;. The CortexM architectures only implement the Thumb instruction set ARMv7M (CortexM3/M4/M7) supports most of "Thumb2 Technology", including conditional execution and encodings for VFP instructions, whereas ARMv6M (CortexM0/M0) only uses Thumb2 in the form of a handful of 4byte system instructions. A forum discussion on Stellarisiti raised the question of how to achieve short delays on a CortexM microcontroller Specifically, delays on the order of cycles, where the overhead of calling a vendorsupplied library routine exceeds the desired delay The difficulty arises from an earlier observation that ARM documents the NOP instruction as being usable only for alignment, and makes no.

Core CortexM4 32bit RISC;. And reduced program memory requirements The CortexM4 instruction set provides the exceptional performance expected of a modern 32bit architecture, with the high code density of 8bit and 16bit microcontrollers The CortexM4 processor closely integrates a configurable Nested Vectored Interrupt. Yeah I have also realized that finding exact cycle accurate simulator that is freely available is quite difficult Thanks for the commercial simulators I am aware of Keil already as I have experience with it But do you know of any freely available simulator that is accurate enough in terms of cycle accuracy (close to actual) for cortexm4?.

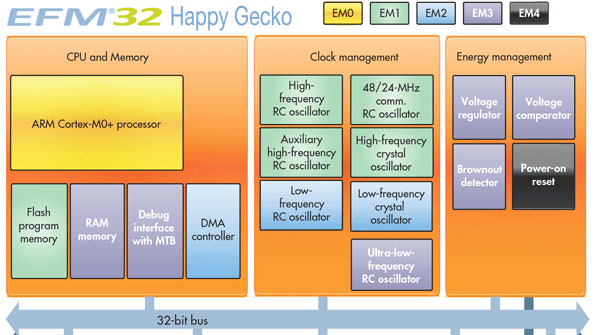

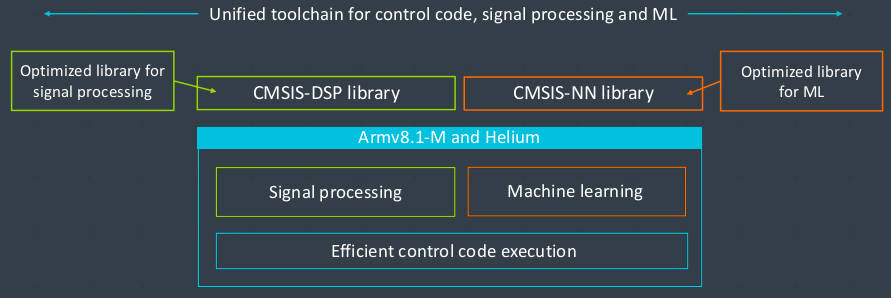

ARM’s Digital Signal Controllers, CortexM4 and CortexM7, address the need for highperformance generic code processing as well as digital signal processing applications The key feature of the CortexM4 and CortexM7 processors is the addition of DSP extensions to the Thumb instruction set, as defined in ARM’s architecture ARMv7M. SAM4S – ARM CortexM4 core;. These devices are designed to be extremely lowpower and are based on the highperformance Arm ® Cortex ®M4 32bit RISC core operating at a frequency of up to 48 MHz This core implements a full set of DSP instructions It is complemented by an Arm ® Cortex ®M0 microcontroller Both cores implement an independent memory protection unit (MPU) that enhances the application security.

ARM Programming Tutorial 10 Thumb Mode vs ARM Mode Instruction Set Duration 1150 Example ARM Cortex M4 Assembly using Keil uVision Duration 953 ENGRTUTOR 12,649 views. The richer CortexM4 instruction set means there’s hardware support for a number of the key operations needed to make the machine learning algorithms run efficiently These instructions are not available on the M0;. The ARM CortexM4 is one of the most powerful microcontrollers on the market and includes a floating point unit (FPU) which enables it to address applications The ARM CortexM4 Microcontroller Cookbook provides a practical introduction to programming an embedded microcontroller architecture.

Floatingpoint Instructions (CortexM4) The CortexM4 processor comes with a FPU coprocessor It provides floatingpoint computation functionality that is compliant with the ANSI/IEEE std , IEEE Standard for Binary FloatingPoint Arithmetic, referred to as the IEEE 754 standard. Binary compatibility with other Cortex processors means that you can use instruction execution time (in cycles) for Thumb instruction set from previous technical reference manuals of ARM CortexM3 or ARM CortexM4 Read more about compatibility in ARM CortexM7 Processor Technical Reference Manual, chapter 231. In this article, we will explain how a function is handled by a microprocessor with examples for ARM CortexM4 It is important to have a basic knowledge of how a function call is handled by the processor Functions make the program more manageable, however, each function call requires additional instructions to be executed.

Joseph Yiu, in The Definitive Guide to ARM® CORTEX®M3 and CORTEX®M4 Processors (Third Edition), 14 313 Instruction set The instruction set used by the Cortex ®M processors is called Thumb (this covers both the 16bit Thumb instructions and the newer 32bit Thumb ® instructions) The CortexM3 and CortexM4 processors incorporate Thumb ®2 Technology, 1 which allow mixture of 16. CORTEXM4 INSTRUCTION TIMING Page 1 of 2 The following information was excerpted from the ARM CortexM4 Processor Technical Reference Manual (r0p1) Basic instruction cycle counts are found in tables 31, 32, and 71 The footnotes were not part of the source document Most common situations highlighted in red From section 333 Load/store. Documentation – Arm Developer.

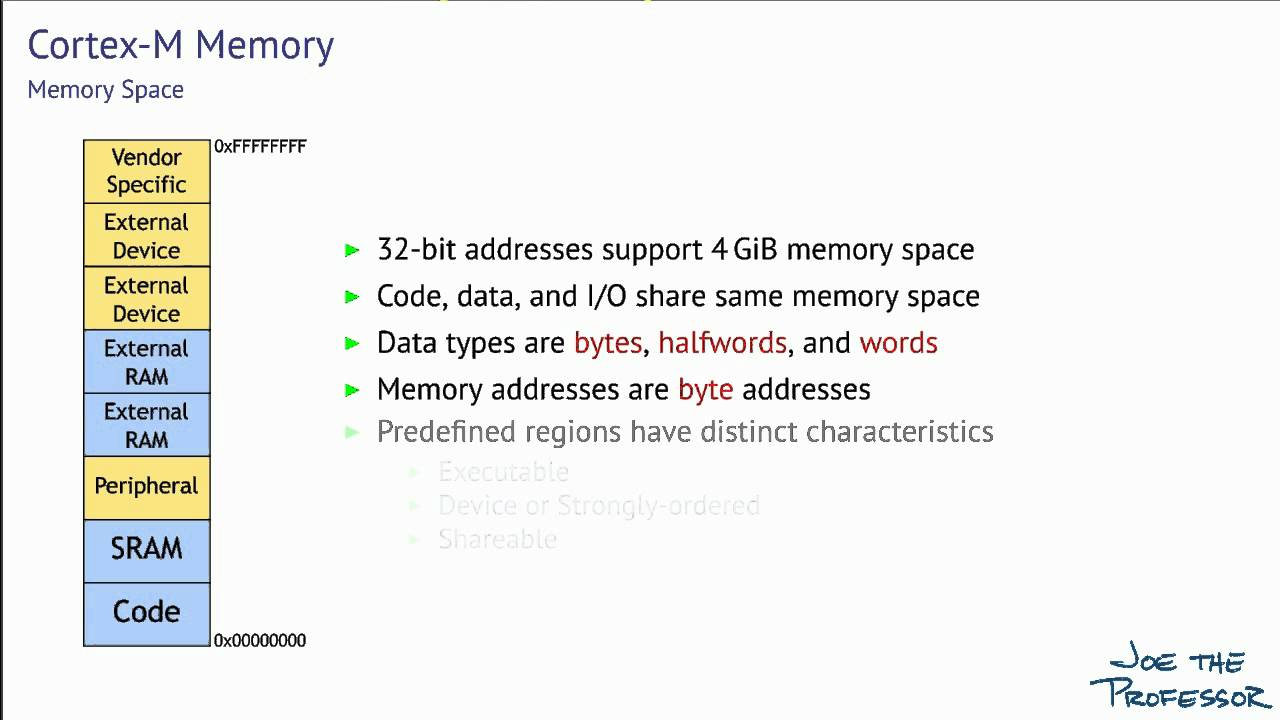

Joseph Yiu, in The Definitive Guide to ARM® CORTEX®M3 and CORTEX®M4 Processors (Third Edition), 14 313 Instruction set The instruction set used by the Cortex ®M processors is called Thumb (this covers both the 16bit Thumb instructions and the newer 32bit Thumb ® instructions) The CortexM3 and CortexM4 processors incorporate Thumb ®2 Technology, 1 which allow mixture of 16. This video presents the basics of the CortexM architecture from the programmer's point of view, including the registers and the memory map. Arm CortexM4 Pdf User Manuals View online or download Arm CortexM4 Generic User Manual.

Important Information for the Arm website This site uses cookies to store information on your computer By continuing to use our site, you consent to our cookies If you are not happy with the use of these cookies, please review our Cookie Policy to learn how they can be disabled By disabling cookies, some features of the site will not work. The STM32 CortexM4 instruction set PM0214 50/260 DocID Rev 5 AND, ANDS {Rd,} Rn, Op2 Logical AND N,Z,C 352 on page 84 ASR, ASRS Rd, Rm, Arithmetic shift right N,Z,C 353 on page 85 B label Branch — 395 on page 141 BFC Rd, #lsb, #width Bit field clear — 391 on page 138 BFI Rd, Rn, #lsb, #width Bit field insert — 391 on page 138. This is a list of microarchitectures based on the ARM family of instruction sets designed by ARM Holdings and 3rd parties, sorted by version of the ARM instruction set, release and name In 05, ARM provided a summary of the numerous vendors who implement ARM cores in their design Keil also provides a somewhat newer summary of vendors of ARM based processors.

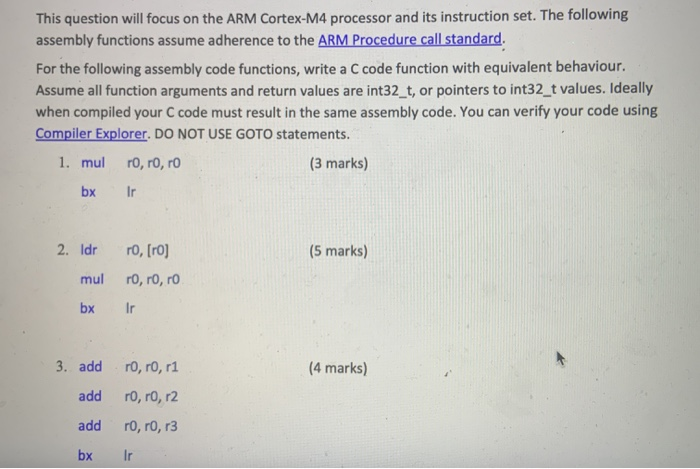

Feature a full set of singlecycle DSP instructions;. Question This Question Will Focus On The ARM CortexM4 Processor And Its Instruction Set The Following Assembly Functions Assume Adherence To The ARM Procedure Call Standard For The Following Assembly Code Functions, Write A C Code Function With Equivalent Behaviour. In this article, we will explain how a function is handled by a microprocessor with examples for ARM CortexM4 It is important to have a basic knowledge of how a function call is handled by the processor Functions make the program more manageable, however, each function call requires additional instructions to be executed.

Built upon the Arm ® Cortex ® M4 core running at 100 or 1 MHz with DSP instruction set and floating point unit, the KV3 devices feature dual 16bit analogtodigital converters (ADCs) sampling at up to 12 mega samples per second (MSPS) in 12bit mode, multiple motor control timers, 64 to 512 KB of flash memory and a comprehensive enablement suite from proprietary and thirdparty resources, including reference designs for ACIM, BLDC and PMSM motor control built on NXP ® 's. About this book ARM CortexM4 Technical Reference Manual (TRM) This manual contains documentation for the CortexM4 processor, the programmer’s model, instruction set, registers, memory map,floating point, multimedia, trace and debug support Product revision status The rmpnidentifier indicates the revision status of the product described in this book, for example, r1p2, where rmIdentifies the major revision of the product, for example, r1 pnIdentifies the minor revision or. Lesson 02 ARM CortexM Instruction Set Floatingpoint Instructions (CortexM4) The CortexM4 processor comes with a FPU coprocessor It provides floatingpoint computation functionality that is compliant with the ANSI/IEEE std , IEEE Standard for Binary FloatingPoint Arithmetic, referred to as the IEEE 754 standard.

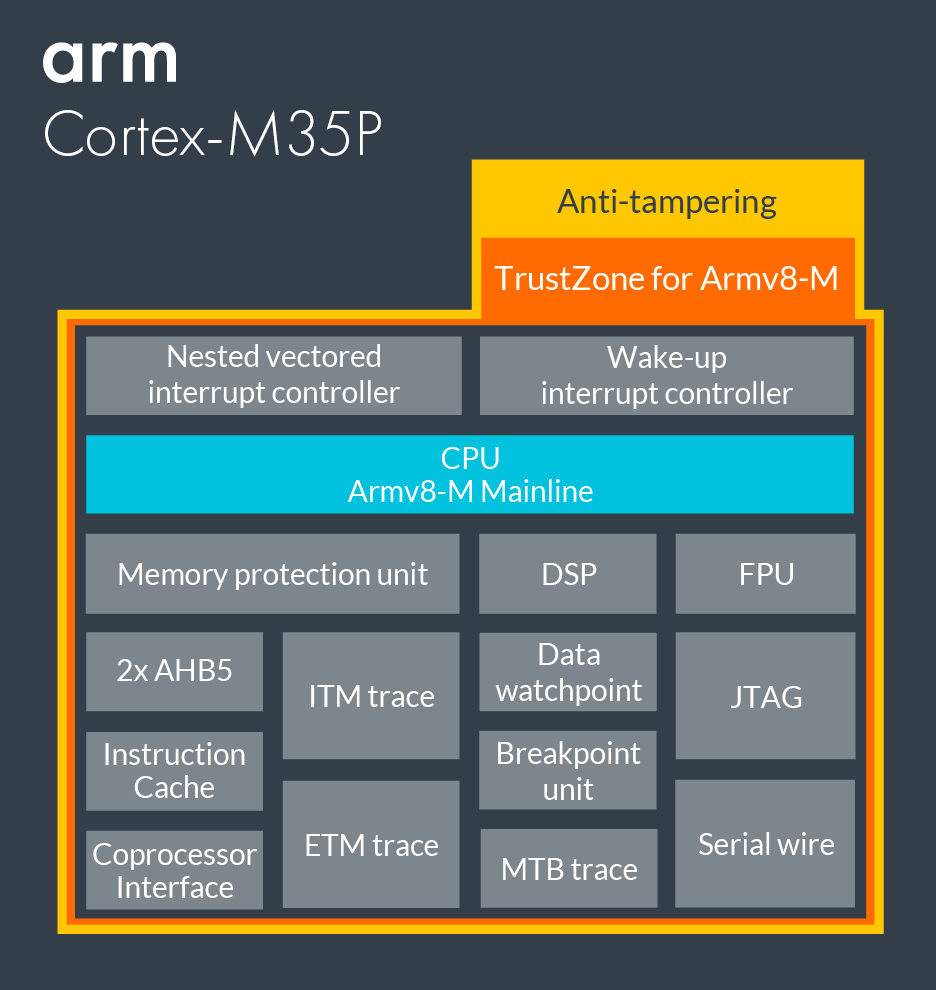

The CortexM3 / M4 / M7 / M33 / M35P have all base Thumb1 and Thumb2 instructions The CortexM3 adds three Thumb1 instructions, all Thumb2 instructions, hardware integer divide, and saturation arithmetic instructions The CortexM4 adds DSP instructions and an optional singleprecision floatingpoint unit (VFPv4SP) The CortexM7 adds an optional doubleprecision FPU (VFPv5). ARM CortexM4 User Guide (link on course web page) ARM Architecture Reference Manual (link on course web page) Arm Processor Arm instruction set outline ELEC 5260/6260/6266 Embedded Systems Describes the details of instruction set, programmer’s model, exception model, and. Operating Frequency 168MHz, 210 DMIPS/125 DMIPS/MHz;.

ARM DDI 0084D ARM Instruction Set This chapter describes the ARM instruction set 41 Instruction Set Summary 42 42 The Condition Field 45 43 Branch and Exchange (BX) 46 44 Branch and Branch with Link (B, BL) 48 45 Data Processing 410 46 PSR Transfer (MRS, MSR) 417 47 Multiply and MultiplyAccumulate (MUL, MLA) 422. 263 Restrictions47 264 ConditionFlags47. Description Access to dedicated SIMD instructions Single Instruction Multiple Data (SIMD) extensions are provided only for CortexM4 and CortexM7 cores to simplify development of application software SIMD extensions increase the processing capability without materially increasing the power consumption.

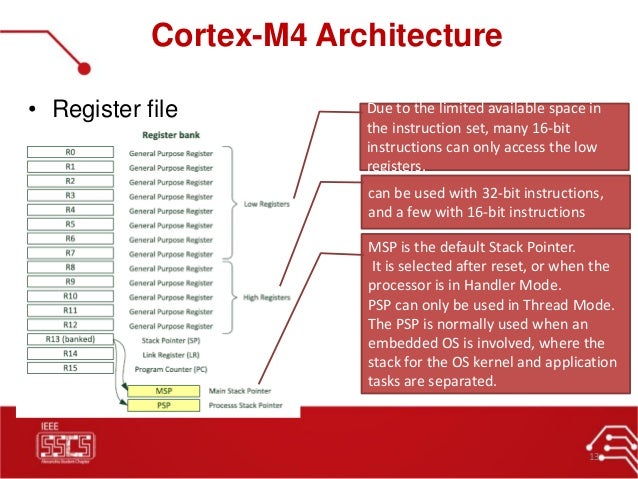

The ARM CortexM4 is one of the most powerful microcontrollers on the market and includes a floating point unit (FPU) which enables it to address applications The ARM CortexM4 Microcontroller Cookbook provides a practical introduction to programming an embedded microcontroller architecture. ARM CortexM4, ARM CortexM7 Microcontroller ARMv8M 32 ARM CortexM23, ARM CortexM33 Microcontroller An optional extension to the ARM instruction set in the ARMv5TE, ARMv5TEJ and ARMv6 architectures VFPv2 has 16 64bit FPU registers VFPv3 or VFPv3D32. CortexM4 Processor Features • 32bit Reduced Instruction Set Computing (RISC) processor • Harvard architecture – Separated data bus and instruction bus • Instruction set – Include the entire Thumb®1 (16bit) and Thumb®2 (16/ 32bit) instruction sets • 3stage branch speculation pipeline • Performance efficiency.

The CortexM4 and CortexM7 share the same system memory map but have quite differing memory systems On a CortexM4 you would expect to see onchip Flash residing at address 0x and onchip SRAM at address 0x However, with the CortexM7 there are two differences in both the instruction and data address region. These devices are designed to be extremely lowpower and are based on the highperformance Arm ® Cortex ®M4 32bit RISC core operating at a frequency of up to 48 MHz This core implements a full set of DSP instructions It is complemented by an Arm ® Cortex ®M0 microcontroller Both cores implement an independent memory protection unit. Because the Cortex M4 only supports the Thumb instruction mode (and not the ARM mode) bit(0) will always be set to 1 by BLX The other option is to use MOV PC, LR but it seems like that is defeating the purpose of the branch instructions On the old ARM CPUs that did not have Thumb mode the MOV PC,LR instruction was the "official" return.

The CortexM architectures only implement the Thumb instruction set ARMv7M (CortexM3/M4/M7) supports most of "Thumb2 Technology", including conditional execution and encodings for VFP instructions, whereas ARMv6M (CortexM0/M0) only uses Thumb2 in the form of a handful of 4byte system instructions. About this book ARM CortexM4 Technical Reference Manual (TRM) This manual contains documentation for the CortexM4 processor, the programmer’s model, instruction set, registers, memory map,floating point, multimedia, trace and debug support Product revision status The rmpnidentifier indicates the revision status of the product described in this book, for example, r1p2, where rmIdentifies the major revision of the product, for example, r1 pnIdentifies the minor revision or. ARM CortexM4 instruction Set Architecture ARM CortexM4 microcontrollers are based on ARMv7 architecture Hence, CortexM4 MCUs support thumb2 instruction set architecture Thumb2 instructions support a mixture of 16bit and 32bit instructions The original architecture of ARM is an ARM instruction set architecture ARM ISA is 32bit long and provides efficient performance.

Comparing this twoinstruction and the previous threeinstruction method, the increase in the size of code from 6 to 8 bytes might have a negative impact on the overall performance so further analysis may be needed before making a choice between the two In ARM state (matic specified CortexM4, just for comparison) this is irrelevant. Documentation – Arm Developer. You can look forward to programming the CortexM4, there are many nice features to explore and benefit from Many instructions only use a single clockcycle, where they use two or more on a CortexM3 That means if you use a large block (or loop), your code might become 3 times as fast per clockcycle.

Because the Cortex M4 only supports the Thumb instruction mode (and not the ARM mode) bit(0) will always be set to 1 by BLX The other option is to use MOV PC, LR but it seems like that is defeating the purpose of the branch instructions On the old ARM CPUs that did not have Thumb mode the MOV PC,LR instruction was the "official" return instruction The disadvantage is that you cannot return to a Thumb function from an ARM function and vice versa. CortexM4 Processor Features • 32bit Reduced Instruction Set Computing (RISC) processor • Harvard architecture – Separated data bus and instruction bus • Instruction set – Include the entire Thumb®1 (16bit) and Thumb®2 (16/ 32bit) instruction sets • 3stage branch speculation pipeline • Performance efficiency. All XMC4000 devices are powered by Arm® Cortex®M4 with a builtin DSP instruction set The Single Precision Floating Point Unit, Direct Memory Access (DMA) feature and Memory Protection Unit (MPU) are stateoftheart for all devices – even the smallest XMC4000 runs with up to 80MHz in core and peripherals.

Floatingpoint Instructions (CortexM4) The CortexM4 processor comes with a FPU coprocessor It provides floatingpoint computation functionality that is compliant with the ANSI/IEEE std , IEEE Standard for Binary FloatingPoint Arithmetic, referred to as the IEEE 754 standard. Question This Question Will Focus On The ARM CortexM4 Processor And Its Instruction Set The Following Assembly Functions Assume Adherence To The ARM Procedure Call Standard For The Following Assembly Code Functions, Write A C Code Function With Equivalent Behaviour. I'm trying to find a reliable method for measuring instruction clock cycles on the STM32F429 MCU that incorporates a CortexM4 processor Part of the challenge is that although the core CPU has no cache, ST added their own proprietary ART Accelerator between the flash memory and the CPU.

2 Number of Instructions I found some documentation surfing the internet to count the number of instructions executed by the arm cortexM3 and cortexM4 # instructions = CYCCNT CPICNT EXCCNT SLEEPCNT LSUCNT FOLDCNT.

Air Supply Lab Lesson 02 Arm Cortex M Instruction Set

Q Tbn And9gcrhnzophx Fr 8sazttvr0fgldv3rrbsoie 9gz1jhotkyotowb Usqp Cau

Arm Cortex M4 Architecture Microcontrollers Programming

Arm Cortex M4 Instruction Set のギャラリー

Arm Cortex M0 Instructions Developer Help

Armv6 M Vs Armv7 M Unpacking The Microcontrollers Processors Blog Processors Arm Community

Arm Cortex M4 Kinetis K 50 Mhz 32 Bit Usb Mcus Nxp

Arm Cortex M4 M7 Advanced Tips 2 Simd Instructions Youtube

Arm Cortex M4 Architecture Microcontrollers Programming

Http Www Sase Com Ar 12 Files 12 09 M0 V6m Q312 Pdf

Notes For Chapter 5 Of The Authoritative Guide To Arm Cortex M3 And Cortex M4 Programmer Sought

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Arm Adds Neural Networking Instructions To Cortex M

Processor Family An Overview Sciencedirect Topics

3 2 17 Richard Kuo Assistant Professor Ppt Video Online Download

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Yiu Joseph Amazon Com Books

The Cortex M0 Challenge Overcoming Technical Barriers Audio Analytic

Arm Cortex M3 Silicon Labs

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Stm32

Cortex M7 Takes Aim At The Iot High Ground Electronic Design

Http Comm Eefocus Com Media Download Index Id

Introduction

Arm Cortex M4 Architecture Microcontrollers Programming

Air Supply Lab Lesson 02 Arm Cortex M Instruction Set

Www Mit Bme Hu Eng System Files Oktatas Targyak Arm Cortex 03 Cortexm0 Cortexm4 Cortexm7 V05 Pdf

The Definitive Guide To The Arm Cortex M3 Yiu Joseph Amazon Com Books

Community Arm Com Cfs File Key Communityserver Blogs Components Weblogfiles 00 00 00 37 85 Cortex 2d00 M For Beginners 2d00 17 5f00 En 5f00 V2 Pdf

Www Mit Bme Hu Eng System Files Oktatas Targyak Arm Cortex 03 Cortexm0 Cortexm4 Cortexm7 V05 Pdf

Architecture And Implementation Of The Arm Cortex A8 Microprocessor

Air Supply Lab Lesson 04 Arm Cortex M Assembly

Chapter 2 Fundamental Concepts

Arm And The Internet Of Things Iot Edn

Architecture And Implementation Of The Arm Cortex A8 Microprocessor

The Cortex M3 M4 Embedded Systems Cortex M3 M4 Instruction Sets Ppt Download

Power Saving Tips When Rapid Prototyping Arm Cortex M Mcus Electronic Design

Arm Microcontrollers And Assembly Programming Processors Blog Processors Arm Community

Which Arm Cortex Cpu Is Right For Your Next Mcu Based Application Digikey

Www Ee Ryerson Ca Courses Ee05 Lectures Arm Cpu Cores Pdf

Which Arm Cortex Cpu Is Right For Your Next Mcu Based Application Digikey

An Introduction To The Armv8 M Architecture Designnews Com

The Cortex M0 Challenge Overcoming Technical Barriers Audio Analytic

Arm Cortex M3 Cortex M4 Assembly Language Programming The Beginners Guide To Arm Cortex M3 And Cortex M4 Processors Learning Upskill Amazon Com Books

Cortex M0 Vs M3 Llvm And Ld Sushihangover

Www Silabs Com Documents Public White Papers Arm Cortex M3 And M4 Mcu Architecture Pdf

Community Arm Com Cfs File Key Telligent Evolution Components Attachments 01 2142 00 00 00 00 52 96 White Paper 2d00 Cortex 2d00 M For Beginners 2d00 16 2800 Final V3 2900 Pdf

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

Arm Cortex M Family Introduction

Chapter 2 Fundamental Concepts

Community Arm Com Cfs File Key Communityserver Blogs Components Weblogfiles 00 00 00 37 85 Cortex 2d00 M For Beginners 2d00 17 5f00 En 5f00 V2 Pdf

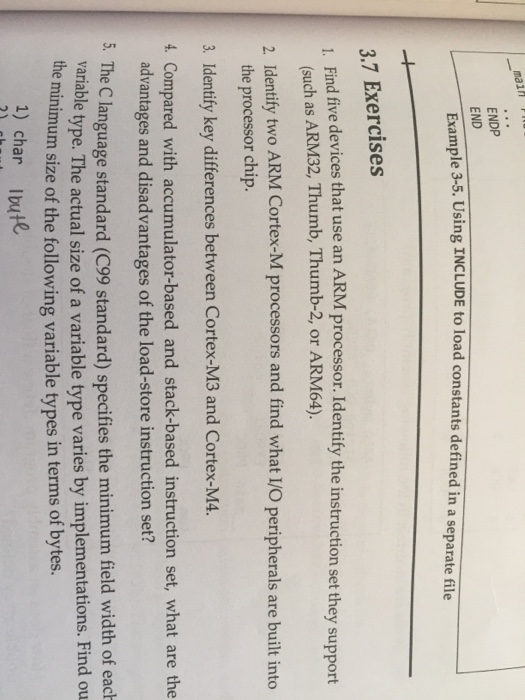

Solved Endp End 3 5 Using Include To Load Constants Defi Chegg Com

This Question Will Focus On The Arm Cortex M4 Proc Chegg Com

Web Sonoma Edu Users F Farahman Sonoma Courses Es310 310 Arm Lectures Chapter 3 And 1 Arm Pdf

Cycle Counting On Arm Cortex M With Dwt Mcu On Eclipse

Catching The String Thoughts On Arm Cortex M Differences

Arm Cortex M4 Specifics

What Is Arm Cortex Quora

Http Ehm Kocaeli Edu Tr Upload Duyurular d2df Pdf

Www Eng Auburn Edu Nelsovp Courses Elec22 Slides Arm prog model 1 Pdf

Arm Cortex M0 Instructions Developer Help

Arm Cortex M4 Microcontrollers Mouser

The Advantages Of Nxp Arm Based Microcontrollers

Typecasting In C Under The Hood With Arm Cortex M4 Assembly

Stm32 Wikipedia

4 How Many Registers Do A Cortex M4 Architecture Chegg Com

Cortexfamily

Arm Adds Neural Networking Instructions To Cortex M

Be Aware Floating Point Operations On Arm Cortex M4f Mcu On Eclipse

Which Clock Source Is Used For Clocking Instructions In Cortex M4 Stack Overflow

01 Arm Cortex M Instruction Set Architecture Youtube

Arm Cortex M4 Core And Tiva C Series Peripherals Springerlink

Designing Advanced Dsp Applications On The Kinetis Arm Cortex

Designing Smart Devices Sydney Iot Meetup 27 8 15

Arm Responds To Risc V And More Ee Times

I Mx Rt1170 Crossover Mcu Family First Ghz Mcu With Arm Cortex M7 And Cortex M4 Cores Nxp

Arm Cortex M For Beginners

Q Tbn And9gcr4 Ctnqikm3 Wvemwrtirp6eiujnv Mc5gnza29npgtkfjah5f Usqp Cau

Arm Architecture Arm Cortex M Microcontroller Stm32 Instruction Set Architecture Arm Architecture Text Material Png Pngegg

Five New Things Cortex M Processors Blog Processors Arm Community

Stm32mp153c Mpu With Arm Dual Cortex 650 Mhz Arm Cortex M4 Real Time Coprocessor Tft Display Fd Can Secure Boot And Cryptography Stmicroelectronics

Cortexfamily

Investigating Arm Cortex M33 Core With Trustzone Dsp Acceleration 1 Mcu On Eclipse

Q Tbn And9gcqz9yff94 Fwfd2jaznlzrukrhenig8qfm5nmhvzhpy1yymw2me Usqp Cau

Arm Architecture Wikipedia

Arm Cortex M Instruction Set Introduction Youtube

Arm Cortex M0 Silicon Labs

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Http Www Sase Com Ar 12 Files 12 09 M0 V6m Q312 Pdf

Ee Bookshelf Arm Cortex M Architecture Overview Adafruit Industries Makers Hackers Artists Designers And Engineers

Http Ccrs Hanyang Ac Kr Webpage Limdj Embedded Cortex M Pdf

Is Armv7 M3 Thumb Instructions Compatible To Armv7 A Thumb Cortex M M Profile Forum Processors Arm Community

Nvic Disabling Interrupts On Arm Cortex M And The Need For A Memory Barrier Instruction Dzone Iot

02 Arm Cortex M4 Specs Ieee Sscs Alexsc

Http Ece Uccs Edu Mwickert Ece5655 Lecture Notes Arm Ece5655 Chap3 Pdf

Stm32l4r9vg Ultra Low Power With Fpu Arm Cortex M4 Mcu 1 Mhz With 1024 Kbytes Of Flash Memory Usb Otg Dfsdm Lcd Tft Mipi Dsi Stmicroelectronics

Q Tbn And9gcta9d4hvkwf8ebwuefkxrlcbndnayycnt1aex7hz ikmocnip Usqp Cau

Arm Cortex M Family Introduction

03 Arm Cortex M Load Store Instructions Youtube

Http Www Armtechforum Com Cn 14 Bj B 1 Bringinghighperformancetothecortex Mprocessorseries Pdf

Arm Cortex M Wikipedia

M7 Processor An Overview Sciencedirect Topics

Cortex M Learning Platform

Stm32f7xx

32 Bit Xmc Industrial Microcontroller Based On Arm Cortex M Infineon Technologies